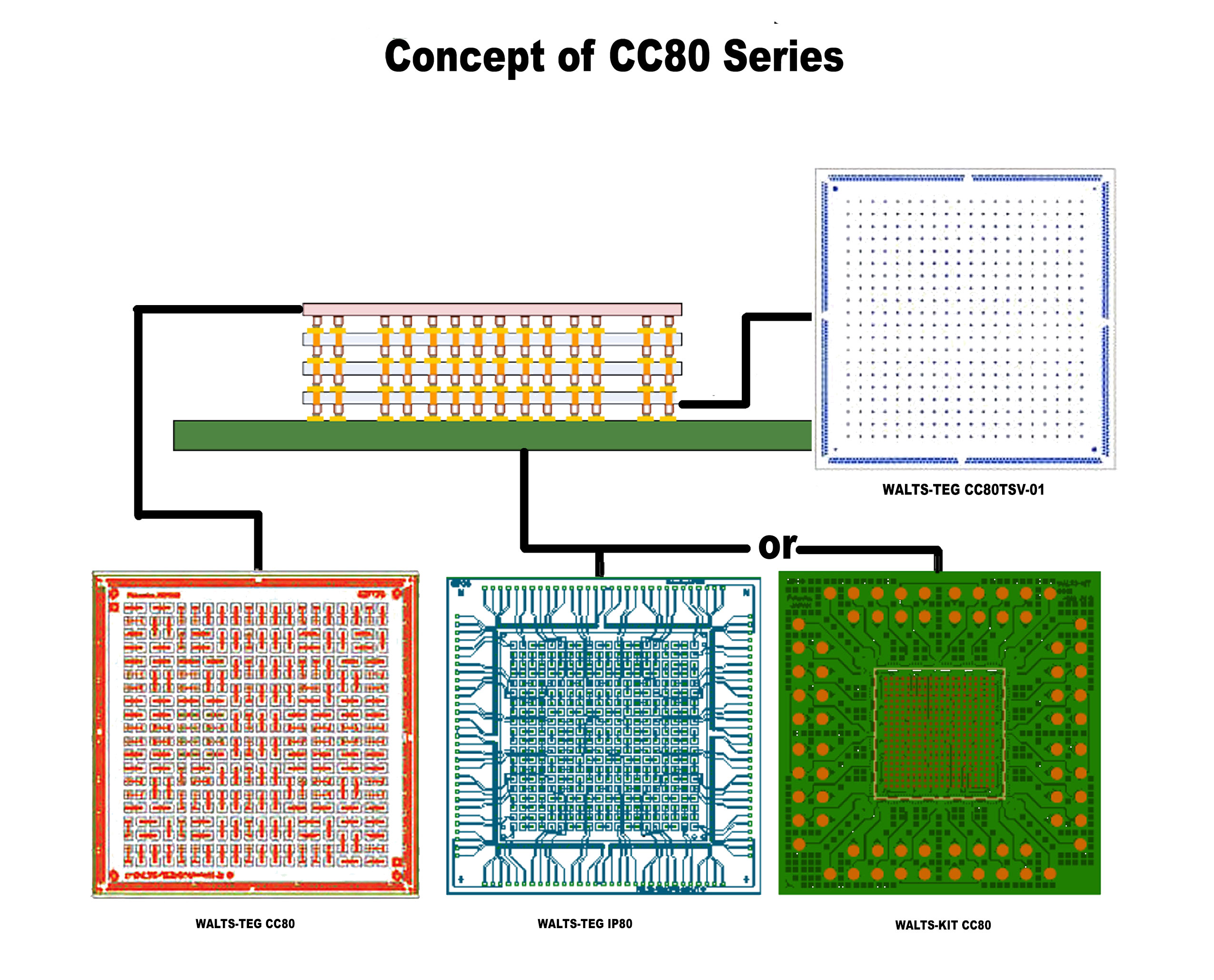

Chip Structure

- Base Layer : P-TEOS*

- Metal Layer : TiN / AI-0.5%Cu

- Passivation Layer : HDP* / P-SiN

*TEOS : Tetraethoxysilane

*HDP : High Density Plasma

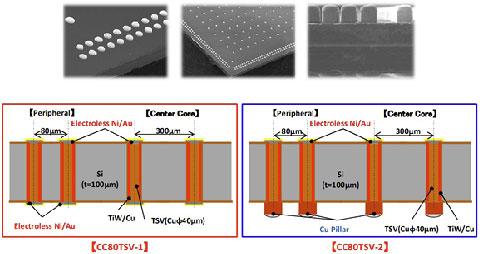

| Specifications | CC80TSV-1 | CC80TSV-2 | ||||||||||||

| Wafer Size | 8 inch | 8 inch | ||||||||||||

| Wafer Thickness | 100μm | 100μm | ||||||||||||

| Chip Size | 7.3mm ♦ | 7.3mm ♦ | ||||||||||||

| Pad pitch | 80μm staggered (Peripheral) 300μm Full area (Center core) |

80μm staggered (Peripheral) 300μm Full area (Center core) |

||||||||||||

| TOP Side |

|

|

||||||||||||

| BOTTOM Side |

|

|

||||||||||||

| Scribe width | 120μm | 120μm | ||||||||||||

| ♦ Bottom Side |